# SB1601 14.5 Gb/s 1-Channel Programmable BERT

**Data Sheet**

#### The BERT Re-imagined

- Complete single channel BERT system

- 14.5 Gb/s with excellent signal fidelity

- Plug & play error detection with built-in CDR

- Flexible, compact and expandable

Remember when BERTs needed two people to lift them? Or when multi-channel meant a huge VXI system that was almost unusable by normal people? We do, and decided it doesn't have to be that way. When you see an SB1601 in real life, you'll be amazed at how small and light it is. However, don't be deceived – this is a high quality, flexible and feature-rich platform designed to be at the heart of any high speed digital testing.

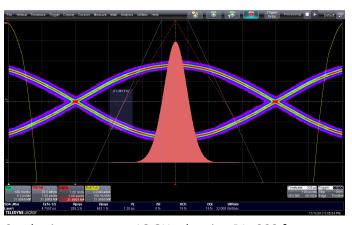

Most test setups start with a high quality test source. Look closely at the front panel and you'll see a high quality 2.92mm connector, the first hint at the impressive output waveform. Fast rise times and low jitter are evident in the high fidelity output eye, ensuring you will measure the performance of your test device, and not your test equipment.

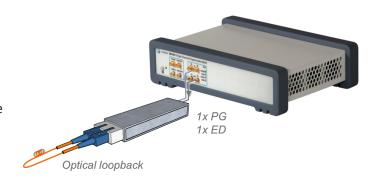

Error detectors used to be hard to set up, with the first challenge being where to get a suitable clock from. Taking usability to new levels, connect to Data In, press Auto-align and you are ready to go - the built in CDR derives a clock typically within 10  $\mu$ s, and the system runs. This doesn't mean that you are limited in ED clocking options - an internal switch means a cable-free pass-over of PG clock if that suits your test needs better.

Usability is key to a fast time-to-productivity, and is designed in from the ground up with the SmarTest SB1601 as we'll see.

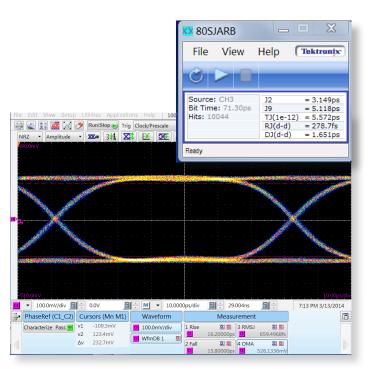

Example PG output at 14.0125 Gb/s, PRBS-31 showing fast rise and fall times, low jitter

### **Applications**

Many test set ups have a BERT at their core for good reason. Whether you are in an R&D lab evaluating silicon, or a transceiver test line in production we have you covered.

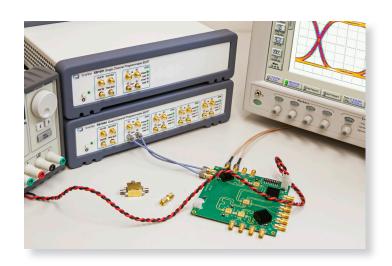

In R&D there are times when you need every corner-case control a BERT was ever equipped with, but more often you just want to get testing fast, and here we shine. With the ability to link several SmarTest BERTs together, testing of parallel backplanes, optical or electrical transceivers and complex ICs just got a whole lot easier. The continuous clock source means easy characterization of maximum data rates up to an impressive 14.5 Gb/s.

Our experience in production environments also shows through with features such as real-time BER display to help TOSA/ROSA alignment operations and many trigger divide ratios enabling sampling scope mask measurements.

Pattern generation and an independent error detector makes transceiver test easy

| Frequency Point | Data Rate (Gb/s) | Standard      |  |

|-----------------|------------------|---------------|--|

| 1               | 1.25             | Ethernet      |  |

| 2               | 2.125            | Fibre Channel |  |

| 3               | 2.5              | Ethernet      |  |

| 4               | 3.125            | XAUI          |  |

| 5               | 4.25             | Fibre Channel |  |

| 6               | 5                | Infiniband    |  |

| 7               | 6                | SATA/SAS      |  |

| 8               | 6.25             | XAUI2         |  |

| 9               | 8.5              | Fibre Channel |  |

| 10              | 9.95328          | Telecom       |  |

| 11              | 10               | Infiniband    |  |

| 12              | 10.3125          | Ethernet      |  |

| 13              | 10.51875         | Fibre Channel |  |

| 14              | 10.70922         | Telecom       |  |

| 15              | 11.181           | Telecom       |  |

| 16              | 11.317           | Fibre Channel |  |

| 17              | 11.5             | Telecom       |  |

| 18              | 12.5             | Ethernet      |  |

| 19              | 12.8             | Telecom       |  |

| 20              | 14.0125          | Fibre Channel |  |

While the system is data rate agile, in addition all common data rates are easily available using built in presets

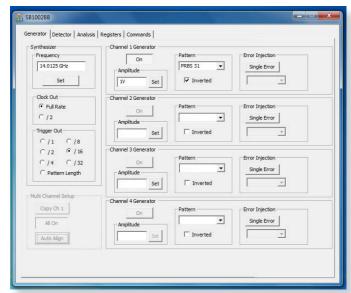

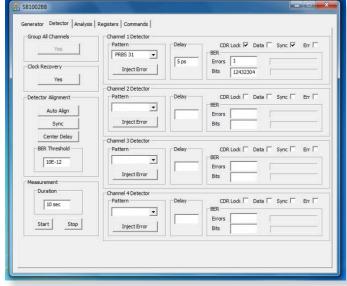

#### **User Interface**

We've put everything you need for the PG on one screen; it's easy to see all operational aspects in one glance, and changes can be made to channels individually, or all together. The same ideas carries through to the ED screen - simple, easy and viewable with one glance. Press Auto Align and the detectors figure the rest out, with easy confirmation on the front panel LEDs. User custom setups can be easily saved and reload for future use.

The graphical user interface may be loaded on any Intel®-based PC running Windows® XP or later, and connects to the SB-series instrument over USB.

Pattern generator setup screen showing fast and simple user interface

Error detector user interface

#### **Built in Flexibility**

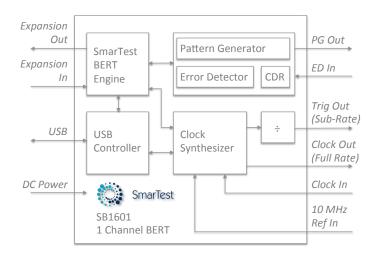

The heart of the SB-series instruments is the SmarTest BERT Engine that powers both PG and ED. An internal synthesizer acts as clock source for the PG, and can be internally switched to also be the ED clock source. Alternatively the ED channel may derive its own clock from the incoming NRZ data stream.

For applications requiring multiple channels, SB-series instruments may be chained together using the Expansion port and special cables (sold separately). This provides sharing of clock and timing as well as communication so that the system may be controlled over a single USB connection from a PC.

SB-series instruments are also available as a 4-channel (SB1604) BERT, and PG-series PG-only (PG1604, PG1601) models.

Internal block diagram with front panel (right) and rear panel (left) connections

Rear panel showing power input (left), USB interface (right) and expansion ports (middle)

## **Specifications**

**Clock System**

Internal Clock

625 MHz to 16 GHz Frequency

Selectable full rate internal clock loopback connection

between PG and ED

Intrinsic RMS jitter

<500 fs typical

External Clock Input

Frequency Full Rate, 625 MHz to 16 GHz

Clock Out

Clock rate Full rate equal to internal

clock setting

**Impedance** 50 Ω nominal, AC-coupled

**Amplitude** 400 mV typical

Connector SMA, single ended, front

panel

Divided Clock / Trigger Out

Clock rate Selectable divided by n, with

n=1, 2, 4, 8, 16, 32, 64

SMA, single ended, Output type

front panel

**Impedance** 50 Ω nominal, AC-coupled

**Amplitude** 400 mV typical

Connector SMA, single ended, front

panel

10 MHz Reference Input

Front panel

Clock to Data Recovery System

Input data rate From 9.95 to 11.3 Gb/s;

14.0125 Gb/s; automatic rate

detection

Type Internal

CDR reference input Internal clock synthesizer or

External Clock Input

CDR loop bandwidth Min: 5.5 MHz

Typical: 8.2 MHz Max: 11.15 MHz

CDR lock time 10 µs typical

Input connector ED data input, front panel

LED on = CDR locked Front panel LED

LED blinking = CDR seeking

lock

**Pattern Generator Specifications**

Number of PG channels

1, front panel connectors

Connector 2.92 mm, differential,

front panel

Front panel LED

Green = channel on

Data output

Differential, AC coupled

Line coding

NRZ

Data rate range

1.25 to 14.5 Gb/s

Output patterns

PRBS 2<sup>n</sup>-1, n=7, 9, 10, 11, 15,

Up to 20 bits/ch, user defined

Pattern invert

Output amplitude 400 - 1,000 mVpp

differential

Rise/fall times

(20%-80%)

< 18 ps typical

Intrinsic jitter (RMS)

< 1 ps typical

Error injection Yes

Synthesizer output at 16 GHz showing RJ <300 fs

## Specifications, continued

| Error Detector Specifications   |                                                                                | General                   |                                                                                                                        |

|---------------------------------|--------------------------------------------------------------------------------|---------------------------|------------------------------------------------------------------------------------------------------------------------|

| Number of ED channels           | 1, front panel connectors                                                      | Control software          | Requires Intel®-based computer running Windows® XP or later                                                            |

| Front panel LED                 | Red = ED no synced,<br>Green = ED synced to input<br>patter, ready to test BER | Interfaces                | USB 2.0 standard,<br>SCPI syntax<br>Exp In, Exp Out proprietary<br>system expansion interfaces                         |

| Data input                      | Differential, AC coupled                                                       |                           |                                                                                                                        |

| Input impedance                 | 100 $\Omega$ differential                                                      | Included power supply     | 100 V to 240 V AC,                                                                                                     |

| Sensitivity                     | 25 mV                                                                          |                           | 50-60 Hz                                                                                                               |

| Line coding                     | NRZ                                                                            | Power consumption         | 150 VA max                                                                                                             |

| Clocking mode                   | Internal CDR                                                                   | Operating temperature     | 0°C to 55°C                                                                                                            |

| Data rate range                 | 1.25 to 14.5 Gb/s                                                              |                           |                                                                                                                        |

| 23, 31                          | PRBS 2 <sup>n</sup> -1, n=7, 9, 10, 11, 15,                                    | Storage temperature       | -30°C to 70°C                                                                                                          |

|                                 | 23, 31<br>Up to 20 bits/ch, user defined                                       | Operating altitude        | Up to 2000 m                                                                                                           |

| Input amplitude<br>ED threshold | 0.1 to 1.0 Vpp Adjustable                                                      | Dimensions<br>(w x h x d) | Bench top Without bumper 10.5 x 7.8 x 2 inches (267 x 198 x 51 mm) With bumper 11.5 x 8 x 3 inches (292 x 203 x 76 mm) |

| Delay range                     | Adjustable                                                                     |                           |                                                                                                                        |

| BER measurement period          | 0 to 10 seconds, 1 ms steps                                                    |                           |                                                                                                                        |

|                                 | BER (instantaneous and accu-                                                   | Weight                    | 4 lbs (1.8 kg)                                                                                                         |

|                                 | mulated, all error count, bit count, time)                                     | Warranty                  | 1 year standard For warranty and calibration                                                                           |

| Connector type SMA, front panel |                                                                                |                           | services, contact SmarTest sales at sales@smartest.us.com                                                              |

## **Included Accessories**

US power cord with external power supply; regional-specific replacement power cord options available

**USB** cable

User guide with programing reference on CD

## **Ordering**

SB1601 1 channel 14.5 Gb/s

integrated pattern generator,

error detector and clock

source

SB1601-3C 3 years total calibration

service, return to factory

SB1601-3W 3 years total warranty

Power cord options - replace US power cord with region-specific one as follows

SB160x-AC-AU Australia

SB160x-AC-CN China

SB160x-AC-EU Europe

SB160x-AC-JP Japan

SB160x-AC-UK United Kingdom

#### About us

We are an experienced group of test professionals with decades of combined experience at some of the biggest companies in the measurement business. We've brought BERTs, oscilloscopes and many other instruments to market for the big guys, but wanted to take high speed testing in a new direction. We're based in the heart of Silicon Valley, California.

The SB1601 paired with the SB1604 multi-channel 14.5 Gb/s BERT

SmarTest, LLC 2005 De La Cruz Boulevard, Suite 195 Santa Clara, CA 95050 USA www.SmarTest.us.com

SB1601EN 14-Mar-14

Copyright © SmarTest, LLC., 2014

All right reserved. SmarTest. Product specifications and descriptions in this document subject to change without notice. Information in this document supersedes that in all previously published material.